EiceDRIVER™

1ED020I12-B2

Single IGBT Driver IC

# Final Data Sheet

Rev. 2.0, 2012-07-31

# **Industrial Power Control**

Edition 2012-07-31

Published by Infineon Technologies AG 81726 Munich, Germany © 2012 Infineon Technologies AG All Rights Reserved.

#### **Legal Disclaimer**

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

| Revision History                                              |       |  |  |  |  |  |

|---------------------------------------------------------------|-------|--|--|--|--|--|

| Page or Item Subjects (major changes since previous revision) |       |  |  |  |  |  |

| Rev. 2.0, 2012-                                               | 07-31 |  |  |  |  |  |

|                                                               |       |  |  |  |  |  |

|                                                               |       |  |  |  |  |  |

|                                                               |       |  |  |  |  |  |

#### Trademarks of Infineon Technologies AG

$AURIX^{\intercal}, BlueMoon^{\intercal}, C166^{\intercal}, CanPAK^{\intercal}, CIPOS^{\intercal}, CIPURSE^{\intercal}, COMNEON^{\intercal}, EconoPACK^{\intercal}, CoolMOS^{\intercal}, CoolSET^{\intercal}, CORECONTROL^{\intercal}, CROSSAVE^{\intercal}, DAVE^{\intercal}, EasyPIM^{\intercal}, EconoBRIDGE^{\intercal}, EconoDUAL^{\intercal}, EconoPIM^{\intercal}, EiceDRIVER^{\intercal}, eupec^{\intercal}, FCOS^{\intercal}, HITFET^{\intercal}, HybridPACK^{\intercal}, I^{2}RF^{\intercal}, ISOFACE^{\intercal}, IsoPACK^{\intercal}, MIPAQ^{\intercal}, ModSTACK^{\intercal}, my-d^{\intercal}, NovalithIC^{\intercal}, OmniTune^{\intercal}, OptiMOS^{\intercal}, ORIGA^{\intercal}, PRIMARION^{\intercal}, PrimePACK^{\intercal}, PrimeSTACK^{\intercal}, PRO-SIL^{\intercal}, PROFET^{\intercal}, RASIC^{\intercal}, ReverSave^{\intercal}, SatRIC^{\intercal}, SIEGET^{\intercal}, SINDRION^{\intercal}, SIPMOS^{\intercal}, SMARTi^{\intercal}, SmartLEWIS^{\intercal}, SOLID FLASH^{\intercal}, TEMPFET^{\intercal}, thinQ!^{\intercal}, TRENCHSTOP^{\intercal}, TriCore^{\intercal}, X-GOLD^{\intercal}, X-PMU^{\intercal}, XMM^{\intercal}, XPOSYS^{\intercal}.$

#### Other Trademarks

Advance Design System™ (ADS) of Agilent Technologies, AMBA™, ARM™, MULTI-ICE™, KEIL™, PRIMECELL™, REALVIEW™, THUMB™, µVision™ of ARM Limited, UK. AUTOSAR™ is licensed by AUTOSAR development partnership. Bluetooth™ of Bluetooth SIG Inc. CAT-iq™ of DECT Forum. COLOSSUS™, FirstGPS™ of Trimble Navigation Ltd. EMV™ of EMVCo, LLC (Visa Holdings Inc.). EPCOS™ of Epcos AG. FLEXGO™ of Microsoft Corporation. FlexRay™ is licensed by FlexRay Consortium. HYPERTERMINAL™ of Hilgraeve Incorporated. IEC™ of Commission Electrotechnique Internationale. IrDA™ of Infrared Data Association Corporation. ISO™ of INTERNATIONAL ORGANIZATION FOR STANDARDIZATION. MATLAB™ of MathWorks, Inc. MAXIM™ of Maxim Integrated Products, Inc. MICROTEC™, NUCLEUS™ of Mentor Graphics Corporation. Mifare™ of NXP. MIPI™ of MIPI Alliance, Inc. MIPS™ of MIPS Technologies, Inc., USA. muRata™ of MURATA MANUFACTURING CO., MICROWAVE OFFICE™ (MWO) of Applied Wave Research Inc., OmniVision™ of OmniVision Technologies, Inc. Openwave™ Openwave Systems Inc. RED HAT™ Red Hat, Inc. RFMD™ RF Micro Devices, Inc. SIRIUS™ of Sirius Satellite Radio Inc. SOLARIS™ of Sun Microsystems, Inc. SPANSION™ of Spansion LLC Ltd. Symbian™ of Symbian Software Limited. TAIYO YUDEN™ of Taiyo Yuden Co. TEAKLITE™ of CEVA, Inc. TEKTRONIX™ of Tektronix Inc. TOKO™ of TOKO KABUSHIKI KAISHA TA. UNIX™ of X/Open Company Limited. VERILOG™, PALLADIUM™ of Cadence Design Systems, Inc. VLYNQ™ of Texas Instruments Incorporated. VXWORKS™, WIND RIVER™ of WIND RIVER SYSTEMS, INC. ZETEX™ of Diodes Zetex Limited.

Last Trademarks Update 2010-10-26

Final Data Sheet 3 Rev. 2.0, 2012-07-31

## **Table of Contents**

|                          | Table of Contents                                                                    | . 4        |

|--------------------------|--------------------------------------------------------------------------------------|------------|

|                          | List of Figures                                                                      | . 5        |

|                          | List of Tables                                                                       | . 6        |

| 1                        | Overview                                                                             | . 7        |

| 2                        | Block Diagram                                                                        | . 9        |

| 3                        | Pin Configuration and Functionality                                                  | 10         |

| 3.1                      | Pin Configuration                                                                    |            |

| 3.2                      | Pin Functionality                                                                    |            |

| 4                        | Functional Description                                                               | 13         |

| 4.1                      | Introduction                                                                         |            |

| 4.2                      | Supply                                                                               |            |

| 4.3                      | Internal Protection Features                                                         |            |

| 4.3.1                    | Undervoltage Lockout (UVLO)                                                          |            |

| 4.3.2                    | READY Status Output                                                                  |            |

| 4.3.3                    | Watchdog Timer                                                                       |            |

| 4.3.4                    | Active Shut-Down                                                                     |            |

| 4.3. <del>4</del><br>4.4 | Non-Inverting and Inverting Inputs                                                   |            |

|                          | Driver Output                                                                        |            |

| 4.5                      | <b>!</b>                                                                             |            |

| 4.6                      | External Protection Features                                                         |            |

| 4.6.1                    | Desaturation Protection                                                              |            |

| 4.6.2                    | Active Miller Clamp                                                                  |            |

| 4.6.3                    | Short Circuit Clamping                                                               |            |

| 4.7                      | RESET                                                                                | 15         |

| 5                        | Electrical Parameters                                                                | 16         |

| 5.1                      | Absolute Maximum Ratings                                                             |            |

| 5.2                      | Operating Parameters                                                                 |            |

| 5.3                      | Recommended Operating Parameters                                                     |            |

| 5.4                      | Electrical Characteristics                                                           |            |

| 5.4.1                    | Voltage Supply                                                                       |            |

| 5.4.2                    | Logic Input and Output                                                               |            |

| 5.4.3                    | Gate Driver                                                                          |            |

| 5.4.4                    | Active Miller Clamp                                                                  |            |

| 5.4.5                    | Short Circuit Clamping                                                               |            |

| 5.4.6                    | , •                                                                                  |            |

|                          | Dynamic Characteristics                                                              |            |

| 5.4.7                    | Desaturation Protection                                                              |            |

| 5.4.8                    | Active Shut Down                                                                     | 22         |

| 6                        | Insulation Characteristics                                                           |            |

| 6.1                      | Certified according to DIN EN 60747-5-2 (VDE 0884 Teil 2): 2003-01. Basic Insulation | 24         |

| 6.2                      | Recognized under UL 1577                                                             | 24         |

| 6.3                      | Reliability                                                                          | 24         |

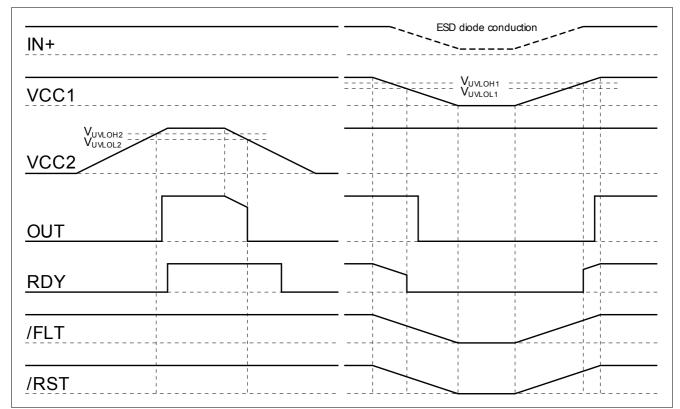

| 7                        | Timing Diagramms                                                                     | 25         |

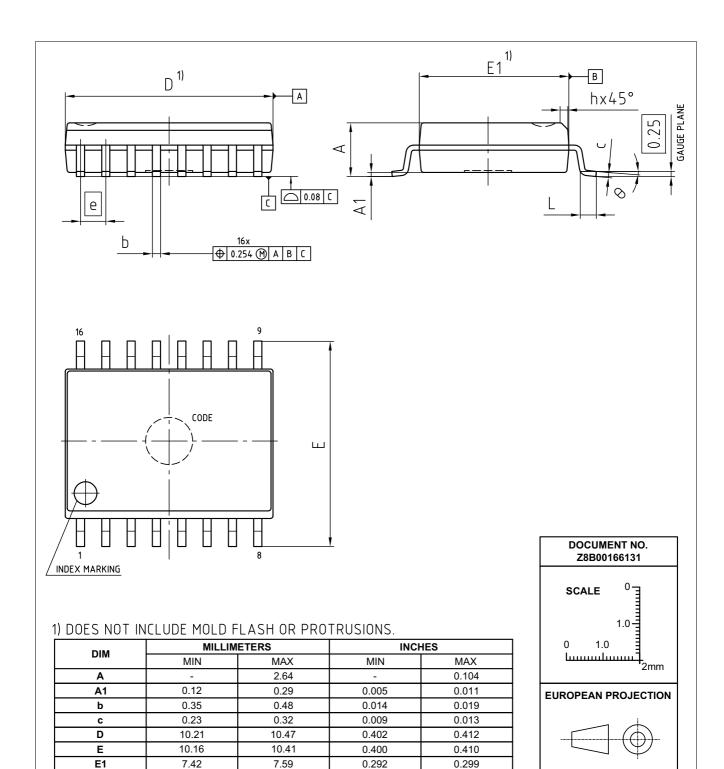

| 8                        | Package Outlines                                                                     | 27         |

| ۵                        | Application Notes                                                                    | 20         |

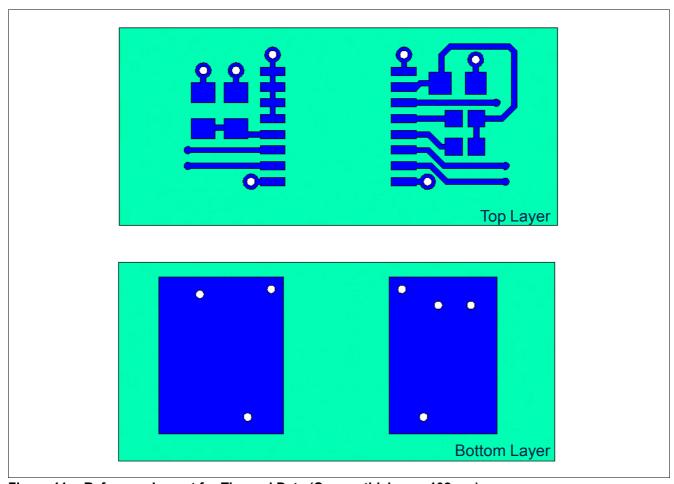

| <b>9</b><br>9.1          | Reference Layout for Thermal Data                                                    |            |

| 9. i<br>9.2              | •                                                                                    | 28         |

| J. Z                     | Finited Circuit Duald Guidelines                                                     | <b>Z</b> Ø |

4

## **List of Figures**

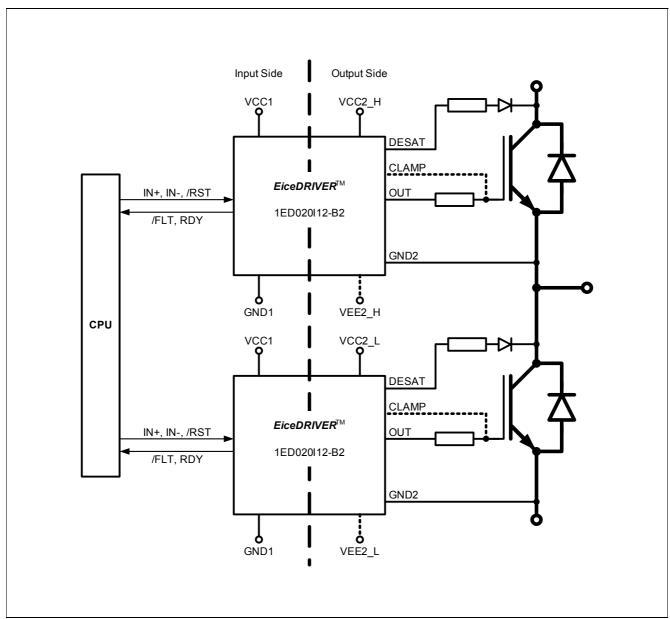

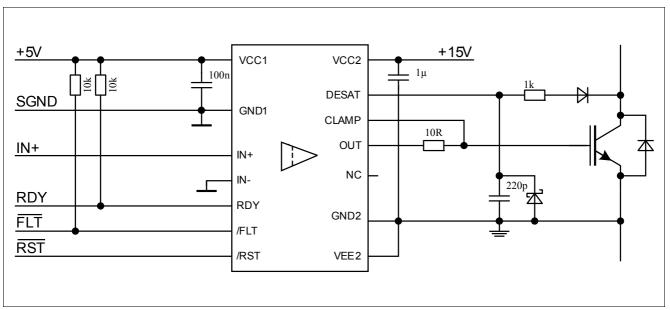

| Figure 1  | Typical Application                                         | 8  |

|-----------|-------------------------------------------------------------|----|

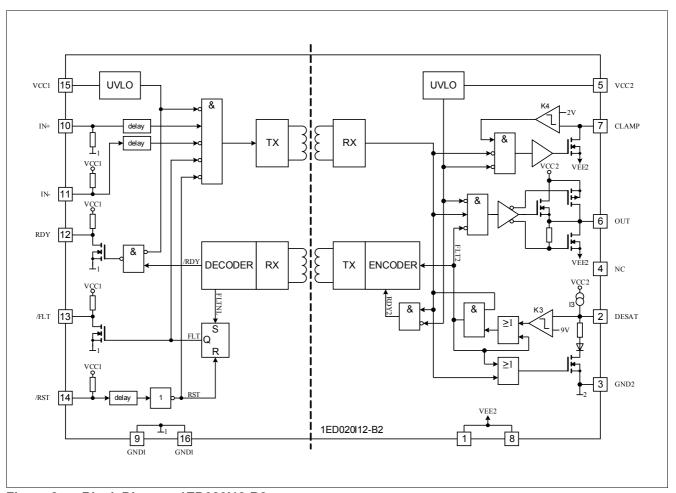

| Figure 2  | Block Diagram 1ED020I12-B2                                  |    |

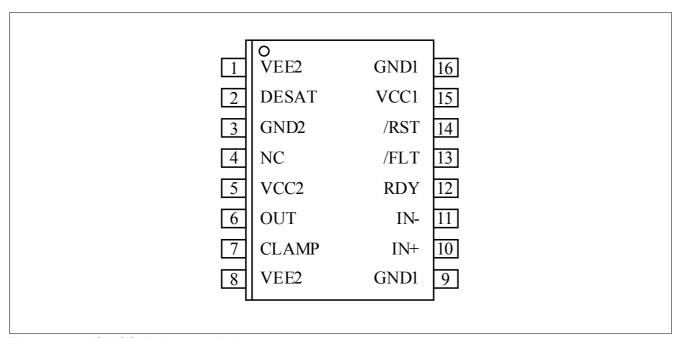

| Figure 3  | PG-DSO-16-15 (top view)                                     |    |

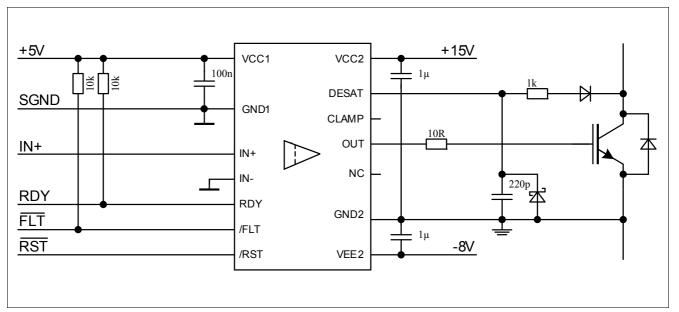

| Figure 4  | Application Example Bipolar Supply                          | 13 |

| Figure 5  | Application Example Unipolar Supply                         | 14 |

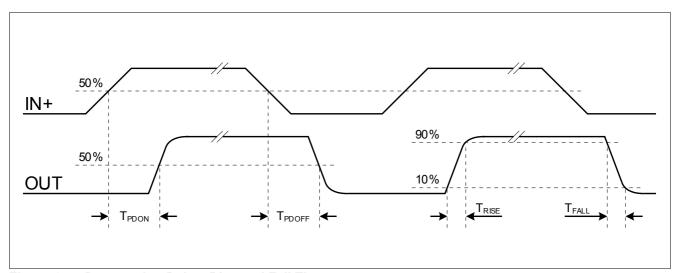

| Figure 6  | Propagation Delay, Rise and Fall Time                       | 25 |

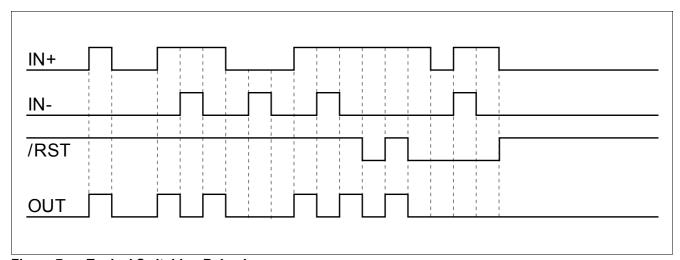

| Figure 7  | Typical Switching Behavior                                  | 25 |

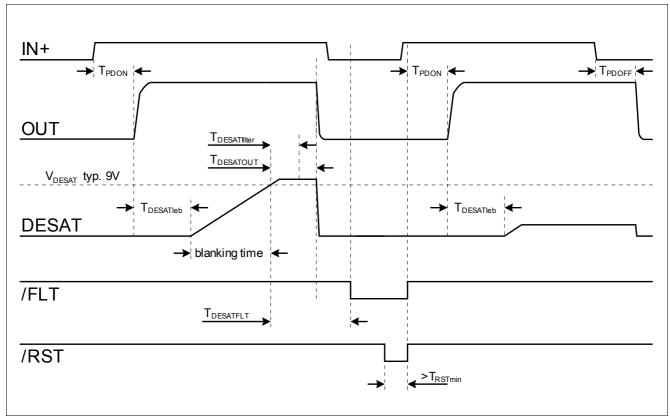

| Figure 8  | DESAT Switch-Off Behavior                                   | 26 |

| Figure 9  | UVLO Behavior                                               | 26 |

| Figure 10 | PG-DSO-16-15 (Plastic (Green) Dual Small Outline Package)   | 27 |

| Figure 11 | Reference Layout for Thermal Data (Copper thickness 102 µm) | 28 |

## **List of Tables**

| Table 1  | Pin Configuration                | 10 |

|----------|----------------------------------|----|

| Table 2  | Absolute Maximum Ratings         | 16 |

| Table 3  | Operating Parameters             | 17 |

| Table 4  | Recommended Operating Parameters | 17 |

| Table 5  | Voltage Supply                   | 18 |

| Table 6  | Logic Input and Output           | 19 |

| Table 7  | Gate Driver                      | 20 |

| Table 8  | Active Miller Clamp              | 20 |

| Table 9  | Short Circuit Clamping           | 21 |

| Table 10 | Dynamic Characteristics          | 21 |

| Table 11 | Desaturation Protection          |    |

| Table 12 | Active Shut Down                 | 23 |

| Table 13 | According to DIN EN 60747-5-2    | 24 |

| Table 14 | Recognized under UL 1577         | 24 |

## EiceDRIVER™ Single IGBT Driver IC

1ED020I12-B2

## 1 Overview

#### **Main Features**

- · Single channel isolated IGBT Driver

- For 600V/1200 V IGBTs

- 2 A rail-to-rail output

- Vcesat-detection

- Active Miller Clamp

#### **Product Highlights**

- Coreless transformer isolated driver

- Basic insulation according to DIN EN 60747-5-2

- Integrated protection features

- Suitable for operation at high ambient temperature

#### **Typical Application**

- · AC and Brushless DC Motor Drives

- High Voltage DC/DC-Converter

- UPS-Systems

- Welding

#### **Description**

The 1ED020I12-B2 is a galvanic isolated single channel IGBT driver in PG-DSO-16-15 package that provides an output current capability of typically 2A.

All logic pins are 5V CMOS compatible and could be directly connected to a microcontroller.

The data transfer across galvanic isolation is realized by the integrated Coreless Transformer Technology.

The 1ED020I12-B2 provides several protection features like IGBT desaturation protection, active Miller clamping and active shut down.

| Product Name | Gate Drive Current | Package      |  |

|--------------|--------------------|--------------|--|

| 1ED020I12-B2 | ±2 A               | PG-DSO-16-15 |  |

Final Data Sheet 7 Rev. 2.0, 2012-07-31

Overview

Figure 1 Typical Application

**Block Diagram**

## 2 Block Diagram

Figure 2 Block Diagram 1ED020l12-B2

Pin Configuration and FunctionalityPin Configuration

## 3 Pin Configuration and Functionality

## 3.1 Pin Configuration

Table 1 Pin Configuration

| Pin No. | Name  | Function                          |

|---------|-------|-----------------------------------|

| 1       | VEE2  | Negative power supply output side |

| 2       | DESAT | Desaturation protection           |

| 3       | GND2  | Signal ground output side         |

| 4       | NC    | Not connected                     |

| 5       | VCC2  | Positive power supply output side |

| 6       | OUT   | Driver output                     |

| 7       | CLAMP | Miller clamping                   |

| 8       | VEE2  | Negative power supply output side |

| 9       | GND1  | Ground input side                 |

| 10      | IN+   | Non inverted driver input         |

| 11      | IN-   | Inverted driver input             |

| 12      | RDY   | Ready output                      |

| 13      | /FLT  | Fault output, low active          |

| 14      | /RST  | Reset input, low active           |

| 15      | VCC1  | Positive power supply input side  |

| 16      | GND1  | Ground input side                 |

Figure 3 PG-DSO-16-15 (top view)

#### Pin Configuration and FunctionalityPin Functionality

## 3.2 Pin Functionality

#### GND<sub>1</sub>

Ground connection of the input side.

#### **IN+ Non Inverting Driver Input**

IN+ control signal for the driver output if IN- is set to low. (The IGBT is on if IN+ = high and IN- = low)

A minimum pulse width is defined to make the IC robust against glitches at IN+. An internal Pull-Down-Resistor ensures IGBT Off-State.

## **IN- Inverting Driver Input**

IN- control signal for driver output if IN+ is set to high. (IGBT is on if IN- = low and IN+ = high)

A minimum pulse width is defined to make the IC robust against glitches at IN-. An internal Pull-Up-Resistor ensures IGBT Off-State.

#### /RST Reset Input

**Function 1**: Enable/shutdown of the input chip. (The IGBT is off if /RST = low). A minimum pulse width is defined to make the IC robust against glitches at /RST.

**Function 2**: Resets the DESAT-FAULT-state of the chip if /RST is low for a time T<sub>RST</sub>. An internal Pull-Up-Resistor is used to ensure /FLT status output.

## /FLT Fault Output

Open-drain output to report a desaturation error of the IGBT (/FLT is low if desaturation occurs)

#### **RDY Ready Status**

Open-drain output to report the correct operation of the device (RDY = high if both chips are above the UVLO level and the internal chip transmission is faultless).

#### VCC1

5 V power supply of the input chip

#### VEE2

Negative power supply pins of the output chip. If no negative supply voltage is available, all VEE2 pins have to be connected to GND2.

#### **DESAT Desaturation Detection Input**

Monitoring of the IGBT saturation voltage ( $V_{CE}$ ) to detect desaturation caused by short circuits. If OUT is high,  $V_{CE}$  is above a defined value and a certain blanking time has expired, the desaturation protection is activated and the IGBT is switched off. The blanking time is adjustable by an external capacitor.

#### **CLAMP Miller Clamping**

Ties the gate voltage to ground after the IGBT has been switched off at a defined voltage to avoid a parasitic switch-on of the IGBT. During turn-off, the gate voltage is monitored and the clamp output is activated when the gate voltage goes below 2 V (related to VEE2). The clamp is designed for a Miller current up to 2 A.

Final Data Sheet 11 Rev. 2.0, 2012-07-31

## Pin Configuration and FunctionalityPin Functionality

#### **GND2 Reference Ground**

Reference ground of the output chip.

### **OUT Driver Output**

Output pin to drive an IGBT. The voltage is switched between VEE2 and VCC2. In normal operating mode Vout is controlled by IN+, IN- and /RST. During error mode (UVLO, internal error or DESAT) Vout is set to VEE2 independent of the input control signals.

#### VCC2

Positive power supply pin of the output side.

#### **Functional DescriptionIntroduction**

## 4 Functional Description

### 4.1 Introduction

The 1ED020I12-B2 is an advanced IGBT gate driver that can be also used for driving power MOS devices. Control and protection functions are included to make possible the design of high reliability systems.

The device consists of two galvanic separated parts. The input chip can be directly connected to a standard 5 V DSP or microcontroller with CMOS in/output and the output chip is connected to the high voltage side.

The rail-to-rail driver output enables the user to provide easy clamping of the IGBTs gate voltage during short circuit of the IGBT. So an increase of short circuit current due to the feedback via the Miller capacitance can be avoided. Further, a rail-to-rail output reduces power dissipation.

The device also includes IGBT desaturation protection with /FLT status output.

The READY status output reports if the device is supplied and operates correctly.

Figure 4 Application Example Bipolar Supply

## 4.2 Supply

The driver 1ED020I12-B2 is designed to support two different supply configurations, bipolar supply and unipolar supply.

In bipolar supply the driver is typically supplied with a positive voltage of 15V at VCC2 and a negative voltage of -8V at VEE2, please refer to **Figure 4**. Negative supply prevents a dynamic turn on due to the additional charge which is generated from IGBT input capacitance times negative supply voltage. If an appropriate negative supply voltage is used, connecting CLAMP to IGBT gate is redundant and therefore typically not necessary.

For unipolar supply configuration the driver is typically supplied with a positive voltage of 15V at VCC2. Erratically dynamic turn on of the IGBT could be prevented with active Miller clamp function, so CLAMP output is directly connected to IGBT gate, please refer to **Figure 5**.

#### **Functional DescriptionInternal Protection Features**

Figure 5 Application Example Unipolar Supply

#### 4.3 Internal Protection Features

## 4.3.1 Undervoltage Lockout (UVLO)

To ensure correct switching of IGBTs the device is equipped with an undervoltage lockout for both chips, refer to **Figure 9**.

If the power supply voltage  $V_{VCC1}$  of the input chip drops below  $V_{UVLOL1}$  a turn-off signal is sent to the output chip before power-down. The IGBT is switched off and the signals at IN+ and IN- are ignored as long as  $V_{VCC1}$  reaches the power-up voltage  $V_{UVLOH1}$ .

If the power supply voltage  $V_{VCC2}$  of the output chip goes down below  $V_{UVLOL2}$  the IGBT is switched off and signals from the input chip are ignored as long as  $V_{VCC2}$  reaches the power-up voltage  $V_{UVLOH2}$ . VEE2 is not monitored, otherwise negative supply voltage range from 0 V to -12 V would not be possible.

### 4.3.2 READY Status Output

The READY output shows the status of three internal protection features.

- UVLO of the input chip

- UVLO of the output chip after a short delay

- Internal signal transmission after a short delay

It is not necessary to reset the READY signal since its state only depends on the status of the former mentioned protection signals.

## 4.3.3 Watchdog Timer

During normal operation the internal signal transmission is monitored by a watchdog timer. If the transmission fails for a given time, the IGBT is switched off and the READY output reports an internal error.

#### 4.3.4 Active Shut-Down

The Active Shut-Down feature ensures a safe IGBT off-state if the output chip is not connected to the power supply, IGBT gate is clamped at OUT to VEE2.

Final Data Sheet 14 Rev. 2.0, 2012-07-31

#### Functional DescriptionNon-Inverting and Inverting Inputs

## 4.4 Non-Inverting and Inverting Inputs

There are two possible input modes to control the IGBT. At non-inverting mode IN+ controls the driver output while IN- is set to low. At inverting mode IN- controls the driver output while IN+ is set to high, please see **Figure 7**. A minimum input pulse width is defined to filter occasional glitches.

## 4.5 Driver Output

The output driver sections uses only MOSFETs to provide a rail-to-rail output. This feature permits that tight control of gate voltage during on-state and short circuit can be maintained as long as the drivers supply is stable. Due to the low internal voltage drop, switching behaviour of the IGBT is predominantly governed by the gate resistor. Furthermore, it reduces the power to be dissipated by the driver.

#### 4.6 External Protection Features

#### 4.6.1 Desaturation Protection

A desaturation protection ensures the protection of the IGBT at short circuit. When the DESAT voltage goes up and reaches 9 V, the output is driven low. Further, the /FLT output is activated, please refer to **Figure 8**. A programmable blanking time is used to allow enough time for IGBT saturation. Blanking time is provided by a highly precise internal current source and an external capacitor.

## 4.6.2 Active Miller Clamp

In a half bridge configuration the switched off IGBT tends to dynamically turn on during turn on phase of the opposite IGBT. A Miller clamp allows sinking the Miller current across a low impedance path in this high dV/dt situation. Therefore in many applications, the use of a negative supply voltage can be avoided.

During turn-off, the gate voltage is monitored and the clamp output is activated when the gate voltage goes below typical 2 V (related to VEE2). The clamp is designed for a Miller current up to 2 A.

### 4.6.3 Short Circuit Clamping

During short circuit the IGBTs gate voltage tends to rise because of the feedback via the Miller capacitance. An additional protection circuit connected to OUT and CLAMP limits this voltage to a value slightly higher than the supply voltage. A current of maximum 500 mA for 10  $\mu$ s may be fed back to the supply through one of this paths. If higher currents are expected or a tighter clamping is desired external Schottky diodes may be added.

#### 4.7 RESET

The reset inputs have two functions.

Firstly, /RST is in charge of setting back the /FLT output. If /RST is low longer than a given time, /FLT will be cleared at the rising edge of /RST, refer to **Figure 8**; otherwise, it will remain unchanged. Moreover, it works as enable/shutdown of the input logic, refer to **Figure 7**.

Final Data Sheet 15 Rev. 2.0, 2012-07-31

## **Electrical Parameters Absolute Maximum Ratings**

## 5 Electrical Parameters

## 5.1 Absolute Maximum Ratings

Note: Absolute maximum ratings are defined as ratings, which when being exceeded may lead to destruction of the integrated circuit. Unless otherwise noted all parameters refer to GND1.

Table 2 Absolute Maximum Ratings

| Parameter                                                        | Symbol         | Va              | lues                                 | Unit | Note /<br>Test Condition          |  |

|------------------------------------------------------------------|----------------|-----------------|--------------------------------------|------|-----------------------------------|--|

|                                                                  |                | Min.            | Max.                                 |      |                                   |  |

| Positive power supply output side                                | $V_{\sf VCC2}$ | -0.3            | 20                                   | V    | 1)                                |  |

| Negative power supply output side                                | $V_{VEE2}$     | -12             | 0.3                                  | V    | 1)                                |  |

| Maximum power supply voltage output side $(V_{VCC2} - V_{VEE2})$ | $V_{max2}$     | _               | 28                                   | V    | -                                 |  |

| Gate driver output                                               | $V_{OUT}$      | $V_{VEE2}$ -0.3 | V <sub>max2</sub> +0.3               | V    | _                                 |  |

| Gate driver high output maximum current                          | $I_{OUT}$      | _               | 2.4                                  | Α    | t = 2 μs                          |  |

| Gate & Clamp driver low output maximum current                   | $I_{OUT}$      | _               | 2.4                                  | А    | t = 2 μs                          |  |

| Maximum short circuit clamping time                              | $t_{CLP}$      | _               | 10                                   | μs   | $I_{\text{CLAMP/OUT}}$ = 500 mA   |  |

| Positive power supply input side                                 | $V_{\sf VCC1}$ | -0.3            | 6.5                                  | V    | _                                 |  |

| Logic input voltages (IN+,IN-,RST)                               | $V_{LogicIN}$  | -0.3            | 6.5                                  | V    | _                                 |  |

| Opendrain Logic output voltage (FLT)                             | $V_{FLT\#}$    | -0.3            | 6.5                                  | V    | _                                 |  |

| Opendrain Logic output voltage (RDY)                             | $V_{RDY}$      | -0.3            | 6.5                                  | V    | _                                 |  |

| Opendrain Logic output current (FLT)                             | $I_{FLT\#}$    | _               | 10                                   | mA   | _                                 |  |

| Opendrain Logic output current (RDY)                             | $I_{RDY}$      | _               | 10                                   | mA   | _                                 |  |

| Pin DESAT voltage                                                | $V_{DESAT}$    | -0.3            | V <sub>VCC2</sub> +0.3               | V    | 1)                                |  |

| Pin CLAMP voltage                                                | $V_{CLAMP}$    | -0.3            | V <sub>VCC2</sub> +0.3 <sup>2)</sup> | V    | 3)                                |  |

| Input to output isolation voltage (GND2)                         | $V_{ISO}$      | -1200           | 1200                                 | V    |                                   |  |

| Junction temperature                                             | $T_{J}$        | -40             | 150                                  | °C   | _                                 |  |

| Storage temperature                                              | $T_{S}$        | -55             | 150                                  | °C   | _                                 |  |

| Power dissipation, per input part                                | $P_{D,IN}$     | _               | 100                                  | mW   | $^{4)}$ @ $T_{A} = 25^{\circ}$ C  |  |

| Power dissipation, per output part                               | $P_{D,OUT}$    | _               | 700                                  | mW   | $^{4)}$ @ $T_{A}$ = 25°C          |  |

| Thermal resistance (Input part)                                  | $R_{THJA,IN}$  | _               | 160                                  | K/W  | $^{4)}$ @ $T_{A}$ = 25°C          |  |

| Thermal resistance (Output chip active)                          | $R_{THJA,OUT}$ | _               | 125                                  | K/W  | $^{4)}$ @ $T_{A}$ = 25°C          |  |

| ESD Capability                                                   | $V_{ESD}$      | _               | 1                                    | kV   | Human Body<br>Model <sup>5)</sup> |  |

<sup>1)</sup> With respect to GND2.

#### **Electrical ParametersOperating Parameters**

- 2) May be exceeded during short circuit clamping.

- 3) With respect to VEE2.

- 4)Output IC power dissipation is derated linearly at 10 mW/°C above 62°C. Input IC power dissipation does not require derating. See **Figure 11** for reference layouts for these thermal data. Thermal performance may change significantly with layout and heat dissipation of components in close proximity.

- 5) According to EIA/JESD22-A114-B (discharging a 100 pF capacitor through a 1.5 k $\Omega$  series resistor).

## 5.2 Operating Parameters

Note: Within the operating range the IC operates as described in the functional description. Unless otherwise noted all parameters refer to GND1.

**Table 3** Operating Parameters

| Parameter                                                                      | Symbol Val        |                 | alues                  | Unit  | Note /         |

|--------------------------------------------------------------------------------|-------------------|-----------------|------------------------|-------|----------------|

|                                                                                |                   | Min.            | Max.                   |       | Test Condition |

| Positive power supply output side                                              | $V_{\text{VCC2}}$ | 13              | 20                     | V     | 1)             |

| Negative power supply output side                                              | $V_{VEE2}$        | -12             | 0                      | V     | 1)             |

| Maximum power supply voltage output side $(V_{\text{VCC2}} - V_{\text{VEE2}})$ | V <sub>max2</sub> | -               | 28                     | V     | -              |

| Positive power supply input side                                               | $V_{\text{VCC1}}$ | 4.5             | 5.5                    | V     | _              |

| Logic input voltages<br>(IN+,IN-,RST)                                          | $V_{LogicIN}$     | -0.3            | 5.5                    | V     | _              |

| Pin CLAMP voltage                                                              | $V_{CLAMP}$       | $V_{VEE2}$ -0.3 | $V_{\text{VCC2}}^{2)}$ | V     | _              |

| Pin DESAT voltage                                                              | $V_{DESAT}$       | -0.3            | $V_{\text{VCC2}}$      | V     | 1)             |

| Pin TLSET voltage                                                              | $V_{TLSET}$       | -0.3            | $V_{VCC2}$             | V     | 1)             |

| Ambient temperature                                                            | $T_{A}$           | -40             | 105                    | °C    | _              |

| Common mode transient immunity <sup>3)</sup>                                   | $ DV_{ISO}/dt $   | _               | 50                     | kV/μs | @ 500 V        |

<sup>1)</sup> With respect to GND2.

## 5.3 Recommended Operating Parameters

Note: Unless otherwise noted all parameters refer to GND1.

Table 4 Recommended Operating Parameters

| Parameter                         | Symbol         | Value | Unit | Note / Test Condition |

|-----------------------------------|----------------|-------|------|-----------------------|

| Positive power supply output side | $V_{\sf VCC2}$ | 15    | V    | 1)                    |

| Negative power supply output side | $V_{\sf VEE2}$ | -8    | V    | 1)                    |

| Positive power supply input side  | $V_{\sf VCC1}$ | 5     | V    | -                     |

<sup>1)</sup> With respect to GND2.

<sup>2)</sup> May be exceeded during short circuit clamping.

<sup>3)</sup> The parameter is not subject to production test - verified by design/characterization

## 5.4 Electrical Characteristics

Note: The electrical characteristics include the spread of values in supply voltages, load and junction temperatures given below. Typical values represent the median values at  $T_A$  = 25°C. Unless otherwise noted all voltages are given with respect to their respective GND (GND1 for pins 9 to 16, GND2 for pins 1 to 8).

## 5.4.1 Voltage Supply

Table 5 Voltage Supply

| Parameter                                                           | Symbol            |      | Values | S    | Unit | Note /                                                                                                                                                                                                                                                 |

|---------------------------------------------------------------------|-------------------|------|--------|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                     |                   | Min. | Тур.   | Max. |      | Test Condition                                                                                                                                                                                                                                         |

| UVLO Threshold Input                                                | $V_{\rm UVLOH1}$  | _    | 4.1    | 4.3  | V    | _                                                                                                                                                                                                                                                      |

| Chip                                                                | $V_{\sf UVLOH1}$  | 3.5  | 3.8    | _    | V    | _                                                                                                                                                                                                                                                      |

| UVLO Hysteresis Input Chip ( $V_{\rm UVLOH1}$ - $V_{\rm UVLOL1}$ )  | V <sub>HYS1</sub> | 0.15 | -      | -    | V    | _                                                                                                                                                                                                                                                      |

| UVLO Threshold Output                                               | $V_{\rm UVLOH2}$  | _    | 12.0   | 12.6 | V    | _                                                                                                                                                                                                                                                      |

| Chip                                                                | $V_{UVLOL2}$      | 10.4 | 11.0   | _    | V    | _                                                                                                                                                                                                                                                      |

| UVLO Hysteresis Output Chip ( $V_{\rm UVLOH1}$ - $V_{\rm UVLOL1}$ ) |                   | 0.7  | 0.9    | -    | V    | -                                                                                                                                                                                                                                                      |

| Quiescent Current Input<br>Chip                                     | $I_{Q1}$          | -    | 7      | 9    | mA   | $V_{\rm VCC1}$ = 5 V<br>IN+ = High,<br>IN- = Low<br>=>OUT = High,<br>RDY = High,<br>/FLT = High                                                                                                                                                        |

| Quiescent Current<br>Output Chip                                    | $I_{\mathrm{Q2}}$ | -    | 4      | 6    | mA   | $\begin{split} V_{\text{VCC2}} &= 15 \text{ V} \\ V_{\text{VEE2}} &= -8 \text{ V} \\ \text{IN+} &= \text{High,} \\ \text{IN-} &= \text{Low} \\ &= > \text{OUT} = \text{High,} \\ \text{RDY} &= \text{High,} \\ /\text{FLT} &= \text{High} \end{split}$ |

## 5.4.2 Logic Input and Output

Table 6 Logic Input and Output

| Parameter                                       | Symbol                                                          |      | Values | 8    | Unit | Note /<br>Test Condition                              |

|-------------------------------------------------|-----------------------------------------------------------------|------|--------|------|------|-------------------------------------------------------|

|                                                 |                                                                 | Min. | Тур.   | Max. |      |                                                       |

| IN+,IN-, RST Low Input Voltage                  | $V_{\mathrm{IN+L}}, \ V_{\mathrm{IN-L}}, \ V_{\mathrm{RSTL\#}}$ | _    | _      | 1.5  | V    | -                                                     |

| IN+,IN-, RST High Input Voltage                 | $V_{\mathrm{IN+H}}, \ V_{\mathrm{IN-H}}, \ V_{\mathrm{RSTH\#}}$ | 3.5  | _      | -    | V    | _                                                     |

| IN-, RST Input Current                          | $I_{IN-},I_{RST\#}$                                             | -400 | -100   | _    | μΑ   | $V_{\mathrm{IN-}}$ = GND1 $V_{\mathrm{RST\#}}$ = GND1 |

| IN+ Input Current                               | $I_{IN+},$                                                      | _    | 100    | 400  | μΑ   | $V_{IN+}$ = VCC1                                      |

| RDY,FLT Pull Up Current                         | $I_{PRDY}, I_{PFLT\#}$                                          | -400 | -100   | -    | μΑ   | $V_{\mathrm{RDY}}$ = GND1 $V_{\mathrm{FLT\#}}$ = GND1 |

| Input Pulse Suppression IN+, IN-                | $T_{\text{MININ+}},$ $T_{\text{MININ-}}$                        | 30   | 40     | _    | ns   | _                                                     |

| Input Pulse Suppression RST for ENABLE/SHUTDOWN | $T_{MINRST}$                                                    | 30   | 40     | _    | ns   | -                                                     |

| Pulse Width RST for Reseting FLT                | $T_{RST}$                                                       | 800  | -      | -    | ns   | -                                                     |

| FLT Low Voltage                                 | $V_{FLTL}$                                                      | _    | _      | 300  | mV   | $I_{SINK(FLT\#)} = 5 \text{ mA}$                      |

| RDY Low Voltage                                 | $V_{RDYL}$                                                      | _    | _      | 300  | mV   | $I_{SINK(RDY)} = 5 \text{ mA}$                        |

## 5.4.3 Gate Driver

Table 7 Gate Driver

| Parameter                         | Symbol      |                       | Values                  |                      |   | Note /                                                                                                                                                                                          |

|-----------------------------------|-------------|-----------------------|-------------------------|----------------------|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                   |             | Min.                  | Тур.                    | Max.                 |   | <b>Test Condition</b>                                                                                                                                                                           |

| High Level Output                 | $V_{OUTH1}$ | V <sub>CC2</sub> -1.2 | V <sub>CC2</sub> -0.8   | _                    | V | I <sub>OUTH</sub> = -20 mA                                                                                                                                                                      |

| Voltage                           | $V_{OUTH2}$ | V <sub>CC2</sub> -2.5 | V <sub>CC2</sub> -2.0   | _                    | V | I <sub>OUTH</sub> = -200 mA                                                                                                                                                                     |

|                                   | $V_{OUTH3}$ | V <sub>CC2</sub> -9   | V <sub>CC2</sub> -5     | _                    | V | I <sub>OUTH</sub> = -1 A                                                                                                                                                                        |

|                                   | $V_{OUTH4}$ |                       | V <sub>CC2</sub> -10    | _                    | V | I <sub>OUTH</sub> = -2 A                                                                                                                                                                        |

| High Level Output Peak<br>Current | $I_{OUTH}$  | -1.5                  | -2.0                    | _                    | A | IN+ = High,<br>IN- = Low;<br>OUT = High                                                                                                                                                         |

| Low Level Output                  | $V_{OUTL1}$ | _                     | V <sub>VEE2</sub> +0.04 | $V_{\rm VEE2}$ +0.09 | V | $I_{\rm OUTL}$ = 20 mA                                                                                                                                                                          |

| Voltage                           | $V_{OUTL2}$ | _                     | V <sub>VEE2</sub> +0.3  | $V_{\rm VEE2}$ +0.85 | V | I <sub>OUTL</sub> = 200 mA                                                                                                                                                                      |

|                                   | $V_{OUTL3}$ | _                     | V <sub>VEE2</sub> +2.1  | $V_{VEE2}$ +5        | V | I <sub>OUTL</sub> = 1 A                                                                                                                                                                         |

|                                   | $V_{OUTL4}$ | _                     | V <sub>VEE2</sub> +7    | _                    | V | <i>I</i> <sub>OUTL</sub> = 2 A                                                                                                                                                                  |

| Low Level Output Peak<br>Current  | $I_{OUTL}$  | 1.5                   | 2.0                     | _                    | A | $\begin{aligned} & \text{IN+} = \text{Low}, \\ & \text{IN-} = \text{Low}; \\ & \text{OUT} = \text{Low}, \\ & V_{\text{VCC2}} = 15 \text{ V}, \\ & V_{\text{VEE2}} = -8 \text{ V} \end{aligned}$ |

## 5.4.4 Active Miller Clamp

Table 8 Active Miller Clamp

| Parameter                  | Symbol        |      | Values                  |                         |   | Note / Test Condition      |

|----------------------------|---------------|------|-------------------------|-------------------------|---|----------------------------|

|                            |               | Min. | Тур.                    | Max.                    |   |                            |

| Low Level Clamp            | $V_{CLAMPL1}$ | _    | V <sub>VEE2</sub> +0.03 | V <sub>VEE2</sub> +0.08 | V | $I_{\rm OUTL}$ = 20 mA     |

| Voltage                    | $V_{CLAMPL2}$ | _    | V <sub>VEE2</sub> +0.3  | V <sub>VEE2</sub> +0.8  | V | I <sub>OUTL</sub> = 200 mA |

|                            | $V_{CLAMPL3}$ | _    | V <sub>VEE2</sub> +1.9  | V <sub>VEE2</sub> +4.8  | V | I <sub>OUTL</sub> = 1 A    |

| Low Level Clamp<br>Current | $I_{CLAMPL}$  | 2    | _                       | _                       | Α | 1)                         |

| Clamp Threshold<br>Voltage | $V_{CLAMP}$   | 1.6  | 2.1                     | 2.4                     | V | Related to VEE2            |

<sup>1)</sup> The parameter is not subject to production test - verified by design/characterization

## 5.4.5 Short Circuit Clamping

Table 9 Short Circuit Clamping

| Parameter                                                         | Symbol            | Values |      |      | Unit | Note /                                                                                                                             |

|-------------------------------------------------------------------|-------------------|--------|------|------|------|------------------------------------------------------------------------------------------------------------------------------------|

|                                                                   |                   | Min.   | Тур. | Max. |      | <b>Test Condition</b>                                                                                                              |

| Clamping voltage (OUT) $(V_{\mathrm{OUT}}$ - $V_{\mathrm{VCC2}})$ | $V_{CLPout}$      | -      | 0.8  | 1.3  | V    | IN+ = High,<br>IN- = Low,<br>OUT = High<br>$I_{\text{OUT}}$ = 500 mA<br>pulse test,<br>$t_{\text{CLPmax}}$ = 10 µs)                |

| Clamping voltage (CLAMP) ( $V_{\rm VCLAMP}$ - $V_{\rm VCC2}$ )    | $V_{ m CLPclamp}$ | -      | 1.3  | -    | V    | IN+ = High, IN- =<br>Low,<br>OUT = High<br>$I_{\rm CLAMP}$ = 500 mA<br>(pulse test,<br>$t_{\rm CLPmax}$ = 10 µs)                   |

| Clamping voltage<br>(CLAMP)                                       | $V_{ m CLPclamp}$ | _      | 0.7  | 1.1  | V    | $ \begin{aligned} \text{IN+ = High, IN- =} \\ \text{Low,} \\ \text{OUT = High} \\ I_{\text{CLAMP}} = 20 \text{ mA} \end{aligned} $ |

## 5.4.6 Dynamic Characteristics

Dynamic characteristics are measured with  $V_{\rm VCC1}$  = 5 V,  $V_{\rm VCC2}$  = 15 V and  $V_{\rm VEE2}$  = -8 V.

Table 10 Dynamic Characteristics

| Parameter                                                                                                        | Symbol        | Values |      |      | Unit | Note /                                                                        |

|------------------------------------------------------------------------------------------------------------------|---------------|--------|------|------|------|-------------------------------------------------------------------------------|

|                                                                                                                  |               | Min.   | Тур. | Max. |      | Test Condition                                                                |

| Input IN+, IN- to output propa-gation delay ON                                                                   | $T_{PDON}$    | 145    | 170  | 195  | ns   | $C_{\mathrm{LOAD}}$ = 100 pF $V_{\mathrm{IN+}}$ = 50%,                        |

| Input IN+, IN- to output propa-gation delay OFF                                                                  | $T_{PDOFF}$   | 145    | 165  | 190  | ns   | V <sub>OUT</sub> =50% @ 25°C                                                  |

| Input IN+, IN- to output propa-gation delay distortion ( $T_{\rm PDOFF}$ - $T_{\rm PDON}$ )                      | $T_{PDISTO}$  | -35    | -5   | 25   | ns   |                                                                               |

| IN+, IN- input to output propagation delay ON variation due to temp                                              | $T_{PDONt}$   | _      | _    | 25   | ns   | $^{1)}C_{\text{LOAD}}$ = 100 pF $V_{\text{IN+}}$ = 50%, $V_{\text{OUT}}$ =50% |

| IN+, IN- input to output<br>propagation delay OFF<br>variation due to temp                                       | $T_{PDOFFt}$  | _      | -    | 40   | ns   | $^{1)}C_{\rm LOAD}$ = 100 pF $V_{\rm IN+}$ = 50%, $V_{\rm OUT}$ =50%          |

| IN+, IN- input to output propagation delay distortion variation due to temp ( $T_{\rm PDOFF}$ - $T_{\rm PDON}$ ) | $T_{PDISTOt}$ | -      | _    | 20   | ns   | $^{1)}C_{\text{LOAD}}$ = 100 pF $V_{\text{IN+}}$ = 50%, $V_{\text{OUT}}$ =50% |

Table 10 Dynamic Characteristics (cont'd)

| Parameter | Symbol     |      | Values |      |    | Note /                                                  |

|-----------|------------|------|--------|------|----|---------------------------------------------------------|

|           |            | Min. | Тур.   | Max. |    | Test Condition                                          |

| Rise Time | $T_{RISE}$ | 10   | 30     | 60   | ns | $C_{\rm LOAD}$ = 1 nF $V_{\rm L}$ 10%, $V_{\rm H}$ 90%  |

|           |            | 200  | 400    | 800  | ns | $C_{\rm LOAD}$ = 34 nF $V_{\rm L}$ 10%, $V_{\rm H}$ 90% |

| Fall Time | $T_{FALL}$ | 10   | 50     | 90   | ns | $C_{\rm LOAD}$ = 1 nF $V_{\rm L}$ 10%, $V_{\rm H}$ 90%  |

|           |            | 200  | 350    | 600  | ns | $C_{\rm LOAD}$ = 34 nF $V_{\rm L}$ 10%, $V_{\rm H}$ 90% |

<sup>1)</sup> The parameter is not subject to production test - verified by design/characterization

## **5.4.7** Desaturation Protection

**Table 11 Desaturation Protection**

| Parameter                            | Symbol            | Values |      |      | Unit | Note /                                                                                                                             |

|--------------------------------------|-------------------|--------|------|------|------|------------------------------------------------------------------------------------------------------------------------------------|

|                                      |                   | Min.   | Тур. | Max. |      | Test Condition                                                                                                                     |

| Blanking Capacitor<br>Charge Current | $I_{DESATC}$      | 450    | 500  | 550  | μΑ   | $V_{\rm VCC2}$ =15 V, $V_{\rm VEE2}$ =- 8 V $V_{\rm DESAT}$ = 2 V                                                                  |

| Blanking Capacitor Discharge Current | $I_{DESATD}$      | 9      | 14   | _    | mA   | $\begin{split} &V_{\text{VCC2}} = 15 \text{ V}, \\ &V_{\text{VEE2}} = -8 \text{ V} \\ &V_{\text{DESAT}} = 6 \text{ V} \end{split}$ |

| Desaturation Reference<br>Level      | $V_{DESAT}$       | 8.3    | 9    | 9.5  | V    | $V_{\rm VCC2}$ = 15 V                                                                                                              |

| Desaturation Filter Time             | $T_{DESATfilter}$ | _      | 250  | _    | ns   | $\begin{split} V_{\text{VCC2}} &= 15 \text{ V}, \\ V_{\text{VEE2}} &= -8 \text{ V} \\ V_{\text{DESAT}} &= 9 \text{ V} \end{split}$ |

| Desaturation Sense to OUT Low Delay  | $T_{DESATOUT}$    | _      | 350  | 430  | ns   | $V_{\rm OUT}$ = 90% $C_{\rm LOAD}$ = 1 nF                                                                                          |

| Desaturation Sense to FLT Low Delay  | $T_{DESATFLT}$    | _      | _    | 2.25 | μs   | $V_{\rm FLT\#}$ = 10%;<br>$I_{\rm FLT\#}$ = 5 mA                                                                                   |

| Desaturation Low<br>Voltage          | $V_{DESATL}$      | 0.4    | 0.6  | 0.95 | V    | IN+ = Low, IN- = Low,<br>OUT = Low                                                                                                 |

| Leading edge blanking                | $T_{DESATleb}$    | _      | 400  | _    | ns   | Not subject of production test                                                                                                     |

## 5.4.8 Active Shut Down

| Parameter                | Symbol                           | Values |      |      | Unit | Note /                                                |  |

|--------------------------|----------------------------------|--------|------|------|------|-------------------------------------------------------|--|

|                          |                                  | Min.   | Тур. | Max. |      | Test Condition                                        |  |

| Active Shut Down Voltage | V <sub>ACTSD</sub> <sup>1)</sup> | _      | _    | 2.0  | V    | $I_{\mathrm{OUT}}$ = -200 mA, $V_{\mathrm{CC2}}$ open |  |

<sup>1)</sup> With reference to VEE2

Insulation CharacteristicsCertified according to DIN EN 60747-5-2 (VDE 0884

## 6 Insulation Characteristics

Insulation characteristics are guaranteed only within the safety maximum ratings which must be ensured by protective circuits in application. Surface mount classification is class A in accordance with CECCOO802.

This coupler is suitable for "basic insulation" only within the safety ratings. Compliance with the safety ratings shall be ensured by means of suitable protective circuits.

# 6.1 Certified according to DIN EN 60747-5-2 (VDE 0884 Teil 2): 2003-01. Basic Insulation

Table 13 According to DIN EN 60747-5-2

| Description                                                                                    | Symbol     | Characteristic    | Unit       |

|------------------------------------------------------------------------------------------------|------------|-------------------|------------|

| Installation classification per EN 60664-1, Table 1                                            |            |                   | _          |

| for rated mains voltage $\leq$ 150 $V_{\rm RMS}$                                               |            | I-IV              |            |

| for rated mains voltage $\leq$ 300 $V_{\rm RMS}$                                               |            | I-III             |            |

| for rated mains voltage $\leq$ 600 $V_{\rm RMS}$                                               |            | I-II              |            |

| Climatic Classification                                                                        |            | 40/105/21         | _          |

| Pollution Degree (EN 60664-1)                                                                  |            | 2                 | _          |

| Minimum External Clearance                                                                     | CLR        | 8.12              | mm         |

| Minimum External Creepage                                                                      | CPG        | 8.24              | mm         |

| Minimum Comparative Tracking Index                                                             | CTI        | 175               | _          |

| Maximum Repetitive Insulation Voltage                                                          | $V_{IORM}$ | 1420              | $V_{PEAK}$ |

| Input to output test voltage, method b <sup>1)</sup>                                           | $V_{PR}$   | 2663              | $V_{PEAK}$ |

| $V_{\rm IORM}$ * 1.875 = $V_{\rm PR}$ , 100% production test with $t_{\rm m}$ = 1 sec,         |            |                   |            |

| partial discharge < 5 pC                                                                       |            |                   |            |

| Input to output test voltage, method a <sup>1)</sup>                                           | $V_{PR}$   | 2272              | $V_{PEAK}$ |

| $V_{\text{IORM}}$ * 1.6 = $V_{\text{PR}}$ , 100% production test with $t_{\text{m}}$ = 60 sec, |            |                   | I LAIK     |

| partial discharge < 5 pC                                                                       |            |                   |            |

| Highest Allowable Overvoltage                                                                  | $V_{IOTM}$ | 6000              | $V_{PEAK}$ |

| Maximum Surge Insulation Voltage                                                               | $V_{IOSM}$ | 6000              | V          |

| Insulation Resistance at $T_{\rm S.}$ $V_{\rm IO}$ = 500 V                                     | $R_{IO}$   | > 10 <sup>9</sup> | Ω          |

| · · · · · · · · · · · · · · · · · · ·                                                          |            |                   |            |

<sup>1)</sup> Refer to VDE 0884 for a detailed description of Method a and Method b partial discharge test profiles.

## 6.2 Recognized under UL 1577

Table 14 Recognized under UL 1577

| Description                          | Symbol    | Characteristic | Unit      |

|--------------------------------------|-----------|----------------|-----------|

| Insulation Withstand Voltage / 1 min | $V_{ISO}$ | 3750           | $V_{rms}$ |

| Insulation Test Voltage / 1 s        | $V_{ISO}$ | 4500           | $V_{rms}$ |

## 6.3 Reliability

For Qualification Report please contact your local Infineon Technologies office.

**Timing DiagrammsReliability**

## 7 Timing Diagramms

Figure 6 Propagation Delay, Rise and Fall Time

Figure 7 Typical Switching Behavior

## **Timing DiagrammsReliability**

Figure 8 DESAT Switch-Off Behavior

Figure 9 UVLO Behavior

Package OutlinesReliability

ISSUE DATE 31.07.2012

**REVISION**

## 8 Package Outlines

Figure 10 PG-DSO-16-15 (Plastic (Green) Dual Small Outline Package)

1.02

0.41

1.27 BSC

0.61

0.25

h

0.024

0.010

0.050 BSC

0.040

0.016

**Application NotesReference Layout for Thermal Data**

## 9 Application Notes

## 9.1 Reference Layout for Thermal Data

The PCB layout shown in **Figure 11** represents the reference layout used for the thermal characterisation. Pins 9 and 16 (GND1) and pins 1 and 8 (VEE2) require ground plane connections for achiving maximum power dissipation. The 1ED020I12-B2 is conceived to dissipate most of the heat generated through this pins.

Figure 11 Reference Layout for Thermal Data (Copper thickness 102 μm)

#### 9.2 Printed Circuit Board Guidelines

Following factors should be taken into account for an optimum PCB layout.

- Sufficient spacing should be kept between high voltage isolated side and low voltage side circuits.

- The same minimum distance between two adjacent high-side isolated parts of the PCB should be maintained to increase the effective isolation and reduce parasitic coupling.

- In order to ensure low supply ripple and clean switching signals, bypass capacitor trace lengths should be kept as short as possible.

- Lowest trace length for VEE2 to GND2 decoupling could be achieved with capacitor closed to pins 1 and 3.

w w w .in fineon.com