# **2SC0650P Description & Application Manual**

Dual-Channel High-Power High-Frequency SCALE-2 Driver Core

#### **Abstract**

The SCALE-2 dual driver core 2SC0650P combines highest power density with broad applicability. The driver is designed for both high-power and high-frequency applications requiring maximum reliability. It is suitable for IGBTs with reverse voltages up to 1700V and also features a dedicated MOSFET mode. The embedded paralleling capability allows easy inverter design covering higher power ratings. Multi-level topologies are also supported.

CONCEPT's patented planar-transformer technology assures efficient and high-voltage isolation with long-term reliability and sets new milestones in compactness, interference immunity and performance. Thanks to its ultra-flat design with an insertion height of max.  $6.5 \, \text{mm}$  and a footprint of  $61.7 \, \text{x}$   $57.2 \, \text{mm}$ , the 2SC0650P can efficiently utilize even the most constrained insertion spaces.

Fig. 1 2SC0650P driver core

## **Contents**

| Abstract                                                          | 1  |

|-------------------------------------------------------------------|----|

| Contents                                                          | 2  |

| Driver Overview                                                   | 4  |

| Mechanical Dimensions                                             | 5  |

| Pin Designation                                                   | 6  |

| Recommended Interface Circuitry for the Primary Side Connector    | 7  |

| Description of Primary Side Interface                             |    |

| General                                                           |    |

| VCC terminal                                                      |    |

| VDC terminal                                                      | 8  |

| MOD (mode selection)                                              | 8  |

| INA, INB (channel drive inputs, e.g. PWM)                         | 9  |

| SO1, SO2 (status outputs)                                         |    |

| TB (input for adjusting the blocking time T <sub>b</sub> )        | 9  |

| Recommended Interface Circuitry for the Secondary Side Connectors | 10 |

| Description of Secondary Side Interfaces                          | 11 |

| General                                                           | 11 |

| DC/DC output (VISOx), emitter (VEx) and COMx terminals            | 11 |

| Reference terminal (REFx)                                         | 11 |

| Collector sense (Vcex)                                            |    |

| Active clamping (ACLx)                                            |    |

| Gate turn-on (GHx) and turn-off (GLx) terminals                   | 13 |

| How Do 2SC0650P SCALE-2 Drivers Work in Detail?                   | 13 |

| Power supply and electrical isolation                             | 13 |

| Power-supply monitoring                                           | 13 |

| IGBT and MOSFET operation mode                                    | 14 |

| V <sub>ce</sub> monitoring / short-circuit protection             |    |

| Desaturation protection with sense diodes                         |    |

| Parallel connection of 2SC0650P                                   |    |

| 3-level or multilevel topologies                                  |    |

| Additional application support for 2SC0650P                       |    |

| BibliographyBibliography                                          | 16 |

| The Information Source: SCALE-2 Driver Data Sheets                | 17 |

| Quite Special: Customized SCALE-2 Drivers                         | 17 |

| Technical Support                | 17 |

|----------------------------------|----|

| Quality                          | 17 |

| Legal Disclaimer                 | 17 |

| Ordering Information             | 18 |

| Information about Other Products | 18 |

| Manufacturer                     | 18 |

#### **Driver Overview**

The 2SC0650P is a driver core equipped with CONCEPT's latest SCALE-2 chipset /1/ as well as newly developed planar transformer technology. The SCALE-2 chipset is a set of application-specific integrated circuits (ASICs) that cover the main range of functions needed to design intelligent gate drivers. The SCALE-2 driver chipset is a further development of the proven SCALE technology /2/.

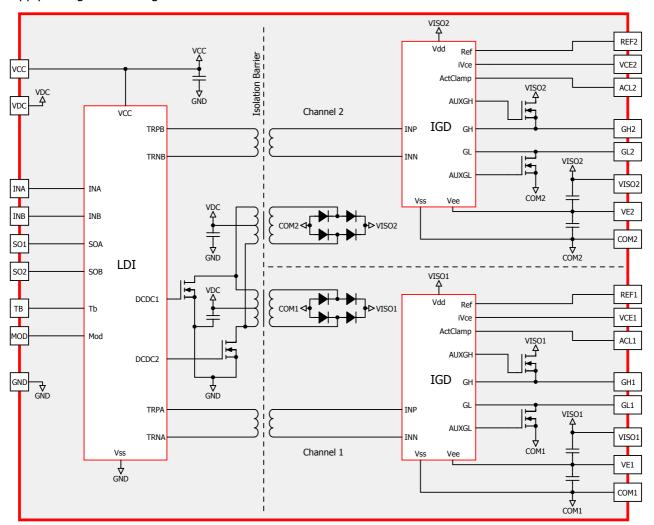

The 2SC0650P targets high-power, dual-channel IGBT and MOSFET applications. The driver supports switching up to 150kHz at best-in-class efficiency. The 2SC0650P comprises a complete dual-channel IGBT driver core, fully equipped with an isolated DC/DC converter, short-circuit protection, advanced active clamping and supply-voltage monitoring.

Fig. 2 Block diagram of the driver core 2SC0650P

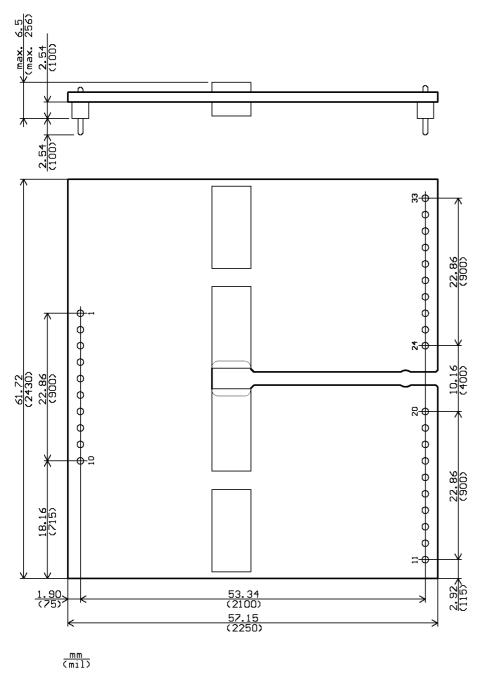

#### **Mechanical Dimensions**

Fig. 3 Mechanical drawing (top view)

The primary side and secondary side pin grid is 2.54mm (100mil) with a pin cross section of 0.64mmx0.64mm. Total outline dimensions of the board are 61.7mmx57.2mm. The total height of the driver is max. 6.5mm measured from the bottom of the pin bodies to the top of the populated PCB.

Recommended diameter of solder pads: Ø 2mm (79 mil) Recommended diameter of drill holes: Ø 1mm (39 mil)

# **Pin Designation**

| Pin No. and Name | Function                                                                            |

|------------------|-------------------------------------------------------------------------------------|

| Primary Side     |                                                                                     |

| 1 GND            | Ground                                                                              |

| 2 VDC            | DC/DC converter supply                                                              |

| 3 SO2            | Status output channel 2; normally high-impedance, pulled down to low on fault       |

| 4 SO1            | Status output channel 1; normally high-impedance, pulled down to low on fault       |

| 5 INB            | Signal input channel 2; non-inverting input relative to GND                         |

| 6 INA            | Signal input channel 1; non-inverting input relative to GND                         |

| 7 MOD            | Mode selection (direct/half-bridge mode)                                            |

| 8 TB             | Set blocking time                                                                   |

| 9 GND            | Ground                                                                              |

| 10 VCC           | Supply voltage; 15V supply for primary side                                         |

| Secondary Sides  |                                                                                     |

| 11 ACL1          | Active clamping feedback channel 1; leave open if not used                          |

| 12 VCE1          | V <sub>ce</sub> sense channel 1; connect to IGBT collector through resistor network |

| 13 REF1          | Set V <sub>ce</sub> detection threshold channel 1; resistor to VE1                  |

| 14 COM1          | Secondary side ground channel 1                                                     |

| 15 VISO1         | DC/DC output channel 1                                                              |

| 16 GH1           | Gate high channel 1; pulls gate high through turn-on resistor                       |

| 17 GH1           | Gate high channel 1; pulls gate high through turn-on resistor                       |

| 18 VE1           | Emitter channel 1; connect to (auxiliary) emitter of power switch                   |

| 19 GL1           | Gate low channel 1; pulls gate low through turn-off resistor                        |

| 20 GL1           | Gate low channel 1; pulls gate low through turn-off resistor                        |

| 21 Free          |                                                                                     |

| 22 Free          |                                                                                     |

| 23 Free          |                                                                                     |

| 24 ACL2          | Active clamping feedback channel 2; leave open if not used                          |

| 25 VCE2          | $V_{\text{ce}}$ sense channel 2; connect to IGBT collector through resistor network |

| 26 REF2          | Set V <sub>ce</sub> detection threshold channel 2; resistor to VE2                  |

| 27 COM2          | Secondary side ground channel 2                                                     |

| 28 VISO2         | DC/DC output channel 2                                                              |

| 29 GH2           | Gate high channel 2; pulls gate high through turn-on resistor                       |

| 30 GH2           | Gate high channel 2; pulls gate high through turn-on resistor                       |

| 31 VE2           | Emitter channel 2; connect to (auxiliary) emitter of power switch                   |

| 32 GL2           | Gate low channel 2; pulls gate low through turn-off resistor                        |

| 33 GL2           | Gate low channel 2; pulls gate low through turn-off resistor                        |

Note: Pins with the designation "Free" are not physically present.

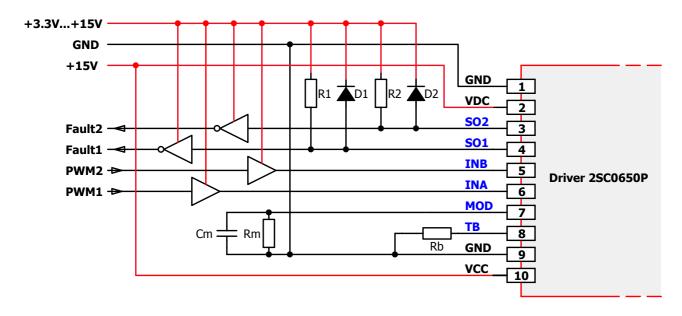

## **Recommended Interface Circuitry for the Primary Side Connector**

Fig. 4 Recommended user interface of 2SC0650P (primary side)

Both ground pins must be connected together with low parasitic inductance. A common ground plane or wide tracks are strongly recommended. The connecting distance between ground pins must be kept at a minimum.

#### **Description of Primary Side Interface**

#### **General**

The primary side interface of the driver 2SC0650P is very simple and easy to use.

The driver primary side is equipped with a 10-pin interface connector with the following terminals:

- 2 x power-supply terminals

- 2 x drive signal inputs

- 2 x status outputs (fault returns)

- 1 x mode selection input (half-bridge mode / direct mode)

- 1 x input to set the blocking time

All inputs and outputs are ESD-protected. Moreover, all digital inputs have Schmitt-trigger characteristics.

#### **VCC terminal**

The driver has one VCC terminal on the interface connector to supply the primary side electronics with 15V.

#### **VDC** terminal

The driver has one VDC terminal on the interface connector to supply the DC-DC converters for the secondary side.

VDC should be supplied with 15V. It is recommended to connect the VCC and VDC terminals to a common +15V power supply. In this case the driver limits the inrush current at startup and no external current limitation of the voltage source for VDC is needed.

### **MOD** (mode selection)

The MOD input allows the operating mode to be selected with a resistor and a capacitor connected to GND.

#### Direct mode

If the MOD input is connected to GND, direct mode is selected. In this mode, there is no interdependence between the two channels. Input INA directly influences channel 1 while INB influences channel 2. High level at an input (INA or INB) always results in turn-on of the corresponding IGBT. In a half-bridge topology, this mode should be selected only when the dead times are generated by the control circuitry so that each IGBT receives its own drive signal.

**Caution:** Synchronous or overlapping timing of both switches of a half-bridge basically shorts the DC link.

#### Half-bridge mode

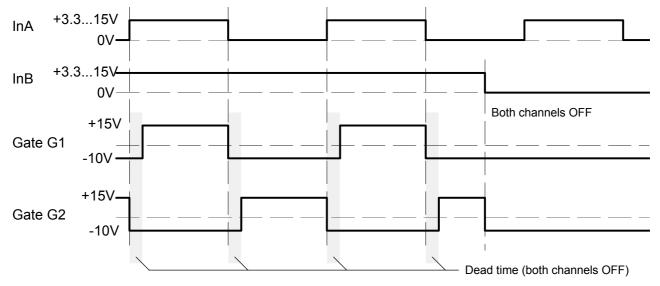

If the MOD input is connected to GND with a resistor  $71k < R_m < 181k$  and a capacitor (recommended value:  $C_m = 22nF$ ), half-bridge mode is selected. In this mode, the inputs INA and INB have the following functions: INA is the drive signal input while INB acts as the enable input (see Fig. 5).

When input INB is low level, both channels are blocked. If it goes high, both channels are enabled and follow the signal on the input INA. At the transition of INA from low to high, channel 2 turns off immediately and channel 1 turns on after a dead time  $T_d$ .

Fig. 5 Signals in half-bridge mode

The value of the dead time  $T_d$  is determined by the value of the resistor  $R_m$  according to the following formula (typical value):

$$R_m[k\Omega] = 31.5 \cdot T_d[\mu s] + 52.7$$

where  $0.6\mu s < T_d < 4.1\mu s$  and  $72k\Omega < R_m < 182k\Omega$

#### INA, INB (channel drive inputs, e.g. PWM)

INA and INB are basically drive inputs, but their function depends on the MOD input (see above). They safely recognize signals in the whole logic-level range between 3.3V and 15V. Both input terminals feature Schmitt-trigger characteristics (refer to the driver data sheet /3/). An input transition is triggered at any edge of an incoming signal at INA or INB.

#### SO1, SO2 (status outputs)

The outputs SOx have open-drain transistors. When no fault condition is detected, the outputs have high impedance. An internal current source of 500µA pulls the SOx outputs to a voltage of about 4V when leaved open. When a fault condition (primary side supply undervoltage, secondary side supply undervoltage, IGBT short-circuit or overcurrent) is detected, the corresponding status output SOx goes to low (connected to GND).

The diodes  $D_1$  and  $D_2$  must be Schottky diodes and must only be used when using 3.3V logic. For 5V...15V logic, they can be omitted.

The maximum SOx current in a fault condition must not exceed the value specified in the driver data sheet /3/.

Both SOx outputs can be connected together to provide a common fault signal (e.g. for one phase). However, it is recommended to evaluate the status signals individually to allow fast and precise fault diagnosis.

#### How the status information is processed

- a) A fault on the secondary side (detection of short-circuit of IGBT module or supply undervoltage) is transmitted to the corresponding SOx output immediately. The SOx output is automatically reset (returning to a high impedance state) after a blocking time  $T_b$  has elapsed (refer to "TB (input for adjusting the blocking time  $T_b$ ) for timing information).

- b) A supply undervoltage on the primary side is indicated to both SOx outputs at the same time. Both SOx outputs are automatically reset (returning to a high impedance state) when the undervoltage on the primary side disappears.

## TB (input for adjusting the blocking time T<sub>b</sub>)

The terminal TB allows the blocking time to be set by connecting a resistor  $R_b$  to GND (see Fig. 4). The following equation calculates the value of  $R_b$  connected between pins TB and GND in order to program the desired blocking time  $T_b$  (typical value):

$$R_b[k\Omega] = 1.0 \cdot T_b[ms] + 51$$

where 20msb<130ms and 71k $\Omega$ b<181k $\Omega$

The blocking time can also be set to a minimum of  $9\mu s$  (typical) by selecting  $R_b=0\Omega$ . The terminal TB must not be left floating.

Note: It is also possible to apply a stabilized voltage at TB. The following equation is used to calculate the voltage  $V_b$  between TB and GND in order to program the desired blocking time  $T_b$  (typical value):

$$V_b[V] = 0.02 \cdot T_b[ms] + 1.02$$

where 20msb<130ms and 1.42b<3.62V

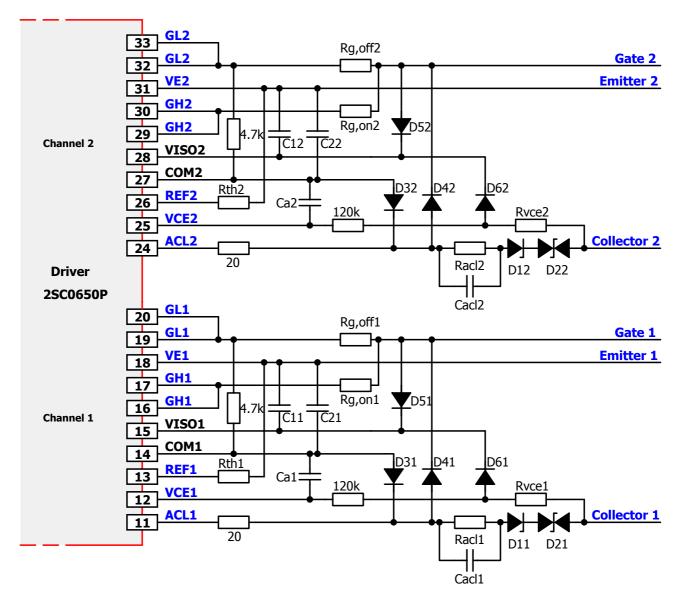

## **Recommended Interface Circuitry for the Secondary Side Connectors**

Fig. 6 Recommended user interface of 2SC0650P with advanced active clamping (secondary sides)

### **Description of Secondary Side Interfaces**

#### General

Each driver's secondary side (driver channel) is equipped with a 10-pin interface connector with the following terminals (x stands for the number of the drive channel 1 or 2):

- 1 x DC/DC output terminal VISOx

- 1 x emitter terminal VEx

- 1 x reference terminal REFx for overcurrent or short-circuit protection

- 1x collector sense terminal VCEx

- 1x active clamping terminal ACLx

- 2x turn-on gate terminals GHx

- 2x turn-off gate terminals GLx

All inputs and outputs are ESD-protected.

#### DC/DC output (VISOx), emitter (VEx) and COMx terminals

The driver is equipped with blocking capacitors on the secondary side of the DC/DC converter (for values, refer to the data sheet /3/).

Power semiconductors with a gate charge of up to  $3\mu C$  can be driven without additional capacitors on the secondary side. For IGBTs or MOSFETs with a higher gate charge, a minimum value of  $3\mu F$  external blocking capacitance is recommended for every  $1\mu C$  gate charge beyond  $3\mu C$ . The blocking capacitors must be placed between VISOx and VEx ( $C_{1x}$  in Fig. 6) as well as between VEx and COMx ( $C_{2x}$  in Fig. 6). They must be connected as close as possible to the driver's terminal pins with minimum inductance. It is recommended to use the same capacitance value for both  $C_{1x}$  and  $C_{2x}$ . Ceramic capacitors with a dielectric strength >20V are recommended.

If the capacitances  $C_{1x}$  or  $C_{2x}$  exceed 150 $\mu F$ , please contact CONCEPT's support service.

No static load must be applied between VISOx and VEx, or between VEx and COMx. A static load can be applied between VISOx and COMx if necessary.

## Reference terminal (REFx)

The reference terminal REFx allows the threshold to be set for short-circuit and/or overcurrent protection with a resistor placed between REFx and VEx. A constant current of 150µA is provided at pin REFx.

### Collector sense (Vcex)

The collector sense must be connected to the IGBT collector or MOSFET drain with the circuit shown in Fig. 6 in order to detect an IGBT or MOSFET overcurrent or short-circuit.

It is recommended to dimension the resistor value of  $R_{vcex}$  in order to get a current of about 0.6-1mA flowing through  $R_{vcex}$  (e.g. 1.2-1.8M $\Omega$  for  $V_{DC-LINK}$ =1200V). The current through  $R_{vcex}$  must not exceed 1mA. It is possible to use a high-voltage resistor as well as series connected resistor. In any case, the min. creepage distance related to the application must be considered.

• The diode  $D_{6x}$  must have a very low leakage current and a blocking voltage of > 40V (e.g. BAS416). Schottky diodes must be explicitly avoided.

For more details about the functionality of this feature and the dimensioning of the response time, refer to " $V_{ce}$  monitoring / short-circuit protection" on page 14.

## Active clamping (ACLx)

Active clamping is a technique designed to partially turn on the power semiconductor as soon as the collectoremitter (drain-source) voltage exceeds a predefined threshold. The power semiconductor is then kept in linear operation.

Basic active clamping topologies implement a single feedback path from the IGBT's collector through transient voltage suppressor devices (TVS) to the IGBT gate. The 2SC0650P supports CONCEPT's advanced active clamping, where the feedback is also provided to the driver's secondary side at pin ACLx: as soon as the voltage on the right side of the  $20\Omega$  resistor (see Fig. 6) exceeds about 1.3V, the turn-off MOSFET is progressively switched off in order to improve the effectiveness of the active clamping and to reduce the losses in the TVS. The turn-off MOSFET is completely off when the voltage on the right side of the  $20\Omega$  resistors (see Fig. 6) approaches 20V (measured to COMx).

It is recommended to use the circuit shown in Fig. 6. The following parameters must be adapted to the application:

- TVS  $D_{1x}$ ,  $D_{2x}$ . It is recommended to use:

- Six 80V TVS with 600V IGBTs with DC link voltages up to 430V. Good clamping results can be obtained with five unidirectional TVS P6SMBJ70A and one bidirectional TVS P6SMBJ70CA from Semikron or with five unidirectional TVS SMBJ70A-E3 and one bidirectional TVS SMBJ70CA-E3 from Vishay.

- Six 150V TVS with 1200V IGBTs with DC link voltages up to 800V. Good clamping results can be obtained with five unidirectional TVS SMBJ130A-E3 and one bidirectional TVS SMBJ130CA-E3 from Vishay or five unidirectional TVS SMBJ130A-TR from ST and one bidirectional TVS P6SMBJ130CA from Diotec.

- Six 220V TVS with 1700V IGBTs with DC link voltages up to 1200V. Good clamping results can be obtained with five unidirectional TVS P6SMB220A and one bidirectional TVS P6SMB220CA from Diotec or five unidirectional TVS SMBJ188A-E3 and one bidirectional TVS SMBJ188CA-E3 from Vishay.

At least one bidirectional TVS ( $D_{2x}$ ) per channel must be used in order to avoid negative current flowing through the TVS chain during turn-on of the antiparallel diode of the IGBT module due to its forward recovery behavior. Such a current could, depending on the application, lead to undervoltage of the driver secondary voltage VISOx to VEx (15V).

Note that it is possible to modify the number of TVS in a chain. The active clamping efficiency can be improved by increasing the number of TVS used in a chain if the total threshold voltage remains at the same value. Note also that the active clamping efficiency is highly dependent on the type of TVS used (e.g. manufacturer).

- $R_{aclx}$  and  $C_{aclx}$ : These parameters allow the effectiveness of the active clamping as well as the losses in the TVS and the IGBT to be optimized. It is recommended to determine the value with measurements in the application. Typical values are:  $R_{aclx}=0...150\Omega$  and  $R_{aclx}*C_{aclx}=100$ ns...500ns.  $R_{aclx}=0\Omega$  is recommended to improve the effectiveness of active clamping.

- $D_{3x}$ ,  $D_{4x}$  and  $D_{5x}$ : it is recommended to use Schottky diodes with blocking voltages >35V (>1A depending on the application).

Please note that the  $20\Omega$  resistor as well as diodes  $D_{3x}$ ,  $D_{4x}$  and  $D_{5x}$  must not be omitted if advanced active clamping is used. If advanced active clamping is not used, the  $20\Omega$  resistor as well as diodes  $D_{3x}$  and  $D_{4x}$  can be omitted.

## Gate turn-on (GHx) and turn-off (GLx) terminals

These terminals allow the turn-on (GHx) and turn-off (GLx) gate resistors to be connected to the gate of the power semiconductor. The GHx and GLx pins are available as separated terminals in order to set the turn-on and turn-off resistors independently without the use of an additional diode. Please refer to the driver data sheet /3/ for the limit values of the gate resistors used. Both terminals GHx and GLx are available on two pins: this allows for a better heat transfer from the driver to the host PCB. Driver cooling can be aided by connecting copper plates to GLx and GHx on the host PCB. However, the load limitations given in the driver data sheet /3/ are valid without additional heat transport over the GHx and GLx pins.

A resistor between GLx and COMx of 4.7k (other values are also possible) may be used in order to provide a low-impedance path from the IGBT/MOSFET gate to the emitter/source even if the driver is not supplied with power. No static load (e.g. resistors) must be placed between GLx and the emitter terminal VEx.

Note however that it is not advisable to operate the power semiconductors within a half-bridge with a driver in the event of a low supply voltage. Otherwise, a high rate of increase of  $V_{ce}$  may cause partial turn-on of these IGBTs.

#### How Do 2SC0650P SCALE-2 Drivers Work in Detail?

## Power supply and electrical isolation

The driver is equipped with a DC/DC converter to provide an electrically insulated power supply to the gate driver circuitry. The signal and power isolation is implemented by newly developed planar transformer technology for a real leap forward in power density, noise immunity, and reliability. Both planar transformers feature safe isolation to EN 50178, protection class II between primary side and either secondary side.

Note that the driver requires a stabilized supply voltage.

#### **Power-supply monitoring**

The driver's primary side as well as both secondary-side driver channels are equipped with a local undervoltage monitoring circuit.

In the event of a primary-side supply undervoltage, the power semiconductors are driven with a negative gate voltage to keep them in the off-state (the driver is blocked) and the fault is transmitted to both outputs SO1 and SO2 until the fault disappears.

In case of a secondary-side supply undervoltage, the corresponding power semiconductor is driven with a negative gate voltage to keep it in the off-state (the channel is blocked) and a fault condition is transmitted to the corresponding SOx output. The SOx output is automatically reset (returning to a high impedance state) after the blocking time.

#### **IGBT and MOSFET operation mode**

The driver features two operation modes:

- The first mode is the default IGBT setup with both a positive (regulated) turn-on voltage of 15V (typical) and a second (non-regulated) turn-off voltage (see Fig. 6).

- The second mode has been specifically designed for ultra-fast MOSFET switching. It incorporates a single turn-on voltage only. The turn-off voltage is set to 0V. This MOSFET mode is activated by connecting the secondary-side terminals COMx and VEx. If 2SC0650P drivers are to be used in the MOSFET mode, please refer to the application note AN-1101 /4/ on www.IGBT-Driver.com/qo/app-note.

## V<sub>ce</sub> monitoring / short-circuit protection

Each channel of the 2SC0650P driver is equipped with a  $V_{ce}$  monitoring circuit. The recommended external circuitry is shown in Fig. 6. A resistor ( $R_{thx}$  in Fig. 6) is used as the reference element for defining the turn-off threshold. The value of the current through  $R_{thx}$  is 150 $\mu$ A (typical). It is recommended to choose threshold levels of about 10V ( $R_{thx}$  values around 68 $\mu$ A). In this case the driver will safely protect the IGBT against short-circuit, but not necessarily against overcurrent. Overcurrent protection has a lower timing priority and is recommended to be realized within the host controller.

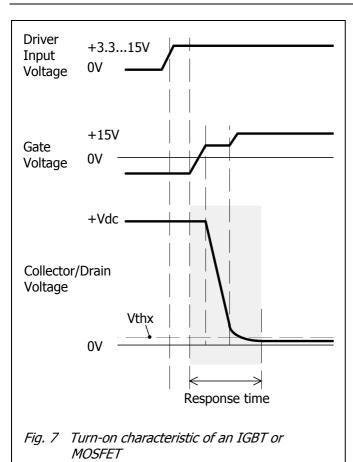

In order to ensure that the 2SC0650P can be applied as universally as possible, the response time capacitor  $C_{ax}$  is not integrated in the driver, but must be connected externally.

During the response time, the  $V_{ce}$  monitoring circuit is inactive. The response time is the time that elapses after turn-on of the power semiconductor until the collector/drain voltage is measured (see Fig. 7).

Both IGBT collector-emitter voltages are measured individually.  $V_{ce}$  is checked after the response time at turn-on to detect a short circuit or overcurrent. If the measured  $V_{ce}$  at the end of the response time is higher than the programmed threshold  $V_{thx}$ , the driver detects a short circuit or overcurrent. The

driver then switches off the corresponding power semiconductor. The fault status is immediately transferred to the corresponding SOx output of the affected channel. The power semiconductor is kept in off state (non-conducting) and the fault is shown at pin SOx as long as the blocking time  $T_b$  is active.

The blocking time  $T_b$  is applied independently to each channel.  $T_b$  starts as soon as  $V_{ce}$  exceeds the threshold of the  $V_{ce}$  monitoring circuit outside the response time span.

The value of the response time capacitors  $C_{ax}$  can be determined with the following table in order to set the desired response time ( $R_{vcex}$ =1.8M $\Omega$ , DC-link voltage  $V_{DC-LINK}$ >550V):

| C <sub>ax</sub> [pF] | $R_{thx} [k\Omega]/V_{thx} [V]$ | Response time [µs] |

|----------------------|---------------------------------|--------------------|

| 0                    | 43 / 6.45                       | 1.2                |

| 15                   | 43 / 6.45                       | 3.2                |

| 22                   | 43 / 6.45                       | 4.2                |

| 33                   | 43 / 6.45                       | 5.8                |

| 47                   | 43 / 6.45                       | 7.8                |

| 0                    | 68 / 10.2                       | 1.5                |

| 15                   | 68 / 10.2                       | 4.9                |

| 22                   | 68 / 10.2                       | 6.5                |

| 33                   | 68 / 10.2                       | 8.9                |

| 47                   | 68 / 10.2                       | 12.2               |

Table 1 Typical response time in function of the capacitance  $C_{ax}$  and the resistance  $R_{thx}$

As the parasitic capacitances on the host PCB may influence the response time it is recommended to measure it in the final design. It is important to define a response time which is smaller than the max. allowed short-circuit duration of the used power semiconductor.

Note that the response time increases at DC-link voltage values lower than 550V and/or higher threshold voltage values  $V_{thx}$ . The response time will decrease at lower threshold voltage values.

## **Desaturation protection with sense diodes**

If desaturation protection with sense diodes is required with 2SC0650P, please refer to the application note AN-1101 /4/ on <a href="https://www.IGBT-Driver.com/go/app-note">www.IGBT-Driver.com/go/app-note</a>.

#### Parallel connection of 2SC0650P

If parallel connection of 2SC0650P drivers is required, please refer to the application note AN-0904 /5/ on <a href="https://www.IGBT-Driver.com/qo/app-note">www.IGBT-Driver.com/qo/app-note</a>.

#### 3-level or multilevel topologies

If 2SC0650P drivers are to be used in 3-level or multilevel topologies, please refer to the application note AN-0901 /6/ on <a href="https://www.IGBT-Driver.com/go/app-note">www.IGBT-Driver.com/go/app-note</a>.

#### Additional application support for 2SC0650P

For additional application support using 2SC0650P drivers, please refer to the application note AN-1101 /4/ on <a href="https://www.IGBT-Driver.com/go/app-note">www.IGBT-Driver.com/go/app-note</a>.

## **Bibliography**

- "Smart Power Chip Tuning", Bodo's Power Systems, May 2007

"Description and Application Manual for SCALE Drivers", CONCEPT

Data sheet SCALE-2 driver core 2SC0650P, CONCEPT

- /4/ Application note AN-1101: Application with SCALE-2 Gate Driver Cores, CONCEPT

- /5/ Application note AN-0904: Direct Paralleling of SCALE-2 Gate Driver Cores, CONCEPT

- /6/ Application note AN-0901: Methodology for Controlling Multi-Level Converter Topologies with SCALE-2 IGBT Drivers, CONCEPT

**Note**: These papers are available on the Internet at <a href="https://www.IGBT-Driver.com/go/papers">www.IGBT-Driver.com/go/papers</a>

#### The Information Source: SCALE-2 Driver Data Sheets

CONCEPT offers the widest selection of gate drivers for power MOSFETs and IGBTs for almost any application requirements. The largest website on gate-drive circuitry anywhere contains all data sheets, application notes and manuals, technical information and support sections: <a href="https://www.IGBT-Driver.com">www.IGBT-Driver.com</a>

#### **Quite Special: Customized SCALE-2 Drivers**

If you need an IGBT driver that is not included in the delivery range, please don't hesitate to contact CONCEPT or your CONCEPT sales partner.

CONCEPT has more than 20 years experience in the development and manufacture of intelligent gate drivers for power MOSFETs and IGBTs and has already implemented a large number of customized solutions.

## **Technical Support**

CONCEPT provides expert help with your questions and problems:

www.IGBT-Driver.com/go/support

#### Quality

The obligation to high quality is one of the central features laid down in the mission statement of CT-Concept Technologie AG. The quality management system covers all stages of product development and production up to delivery. The drivers of the SCALE-2 series are manufactured to the ISO9001:2000 quality standard.

#### **Legal Disclaimer**

This data sheet specifies devices but cannot promise to deliver any specific characteristics. No warranty or guarantee is given – either expressly or implicitly – regarding delivery, performance or suitability.

CT-Concept Technologie AG reserves the right to make modifications to its technical data and product specifications at any time without prior notice. The general terms and conditions of delivery of CT-Concept Technologie AG apply.

## **Ordering Information**

The general terms and conditions of delivery of CT-Concept Technologie AG apply.

Type Designation Description

2SC0650P2A0-17 Dual-channel SCALE-2 driver core

Product home page: <a href="https://www.IGBT-Driver.com/go/2SC0650P">www.IGBT-Driver.com/go/2SC0650P</a>

Refer to www.IGBT-Driver.com/qo/nomenclature for information on driver nomenclature

#### **Information about Other Products**

#### For other driver cores:

Direct link: <a href="https://www.IGBT-Driver.com/qo/cores">www.IGBT-Driver.com/qo/cores</a>

#### For other drivers, product documentation, evaluation systems and application support

Please click onto: www.IGBT-Driver.com

#### **Manufacturer**

CT-Concept Technologie AG Intelligent Power Electronics Renferstrasse 15 CH-2504 Biel-Bienne Switzerland

Tel. +41 - 32 - 344 47 47 Fax +41 - 32 - 344 47 40

E-mail <u>Info@IGBT-Driver.com</u> Internet <u>www.IGBT-Driver.com</u>

© 2009...2011 CT-Concept Technologie AG - Switzerland.

We reserve the right to make any technical modifications without prior notice.

All rights reserved. Version of 2011-08-09